The CBSR receiver is one of the main components of the ground segment of the communication system (i.e. ground station). It is implemented using Software Defined Radio technique, however, both "hardware oriented" and "software oriented" versions will be developed for system flexibility. In this document the electrical and mechanical design of all versions are discussed along with implementation aspects.

# Contents

| List of ac | cronyms                                                                   | 4  |

|------------|---------------------------------------------------------------------------|----|

| 1. Moo     | dule Characteristics                                                      | 5  |

| 1.1.       | General Parameters                                                        | 5  |

| 1.2.       | Implementation                                                            | 5  |

| 1.2.1.     | "Hardware oriented" version                                               | 5  |

| 1.2.2.     | "Software oriented" version                                               | 5  |

| 2. Mo      | dule Electrical Design - "hardware oriented" version                      | 6  |

| 2.1.       | ADRV9361 based receiver                                                   | 6  |

| 2.2.       | Xilinx Zynq Mini-ITX based receiver                                       | 9  |

| 3. Moo     | dule Electrical Design - "software oriented" version                      | 11 |

| 3.1.       | USRP B210 hardware platform []                                            | 11 |

| 4. Rec     | eiver implementation – PL part (FPGA) for "hardware oriented" version     | 12 |

| 4.1.       | Simulink model                                                            | 12 |

| 4.1.1.     | Matched Filtering                                                         | 16 |

| 4.1.2.     | Time synchronization                                                      | 16 |

| 4.1.3.     | Coarse Frequency offset estimation                                        | 17 |

| 4.1.4.     | Coding rate evaluation                                                    |    |

| 4.1.5.     | Radio frame disassembly                                                   | 19 |

| 4.1.6.     | Fine phase and frequency offset estimation                                | 21 |

| 4.1.7.     | Demodulation                                                              | 22 |

| 4.1.8.     | Decoding                                                                  | 22 |

| 4.1.9.     | Data packing                                                              | 23 |

| 4.2.       | Custom-made IP cores                                                      | 24 |

| 4.2.1.     | Introduction                                                              | 24 |

| 4.2.2.     | Reference design customization                                            | 24 |

| 4.2.3.     | The use of Simulink HDL Workflow Advisor                                  | 27 |

| 4.2.4.     | Vivado project details                                                    | 30 |

| 5. Rec     | eiver implementation – PS part (software) for "hardware oriented" version | 32 |

| 5.1.       | TX vs RX – disambiguation                                                 | 32 |

| 5.2.       | Operating System                                                          | 32 |

| 5.2.1.     | Cross-compiling Tools                                                     | 32 |

| 5.2.2.     | Shell                                                                     | 32 |

| 5.2.3.     | Kernel Configuration                                                      | 32 |

| 5.2.4.     | FPGA Driver and Kernel Modules                                            |    |

| 5.2.4.1.                                                                                                                                                                                                           | Driver Attributes Description                                                                                                                                                                                                                                                                                                                                  | . 33                                                                                         |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|

| 5.2.4.2.                                                                                                                                                                                                           | Kernel Modules Loading                                                                                                                                                                                                                                                                                                                                         | . 33                                                                                         |

| 5.2.4.2.1                                                                                                                                                                                                          | . Modules configuration file                                                                                                                                                                                                                                                                                                                                   | . 35                                                                                         |

| 5.2.5.                                                                                                                                                                                                             | Libraries and Tools                                                                                                                                                                                                                                                                                                                                            | . 35                                                                                         |

| 5.2.6.                                                                                                                                                                                                             | Device Tree and Node Configuration                                                                                                                                                                                                                                                                                                                             | . 36                                                                                         |

| 5.2.7.                                                                                                                                                                                                             | RF Configuration                                                                                                                                                                                                                                                                                                                                               | . 37                                                                                         |

| 5.2.8.                                                                                                                                                                                                             | Application Configuration Files                                                                                                                                                                                                                                                                                                                                | . 37                                                                                         |

| 5.2.9.                                                                                                                                                                                                             | Pre-O/S Components and Boot Sequence / Order                                                                                                                                                                                                                                                                                                                   | . 38                                                                                         |

| 5.2.9.1.                                                                                                                                                                                                           | FSBL                                                                                                                                                                                                                                                                                                                                                           | . 38                                                                                         |

| 5.2.9.1.1                                                                                                                                                                                                          | . FSBL Boot Logs                                                                                                                                                                                                                                                                                                                                               | . 38                                                                                         |

| 5.2.9.2.                                                                                                                                                                                                           | SSBL / U-boot                                                                                                                                                                                                                                                                                                                                                  | . 38                                                                                         |

| 5.2.9.3.                                                                                                                                                                                                           | Linux Kernel                                                                                                                                                                                                                                                                                                                                                   | . 39                                                                                         |

| 5.3. C                                                                                                                                                                                                             | ustom Made Applications                                                                                                                                                                                                                                                                                                                                        | . 41                                                                                         |

| 5.3.1.                                                                                                                                                                                                             | Application: ad9361-config.run [TX + RX]                                                                                                                                                                                                                                                                                                                       | . 41                                                                                         |

|                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                |                                                                                              |

| 6. Receiv                                                                                                                                                                                                          | er implementation – "software oriented" version                                                                                                                                                                                                                                                                                                                | . 44                                                                                         |

|                                                                                                                                                                                                                    | er implementation – "software oriented" version<br>nuRadio platform                                                                                                                                                                                                                                                                                            |                                                                                              |

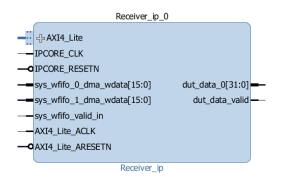

| 6.1. G                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                | . 44                                                                                         |

| 6.1. G<br>6.2. R                                                                                                                                                                                                   | nuRadio platform                                                                                                                                                                                                                                                                                                                                               | . 44<br>. 45                                                                                 |

| 6.1. G<br>6.2. R                                                                                                                                                                                                   | nuRadio platform<br>eceiver architecture                                                                                                                                                                                                                                                                                                                       | . 44<br>. 45<br>. 45                                                                         |

| 6.1. G<br>6.2. R<br>6.3. C                                                                                                                                                                                         | nuRadio platform<br>eceiver architecture<br>ustom-made processing blocks                                                                                                                                                                                                                                                                                       | . 44<br>. 45<br>. 45<br>. 45                                                                 |

| <ul> <li>6.1. G</li> <li>6.2. R</li> <li>6.3. C</li> <li>6.3.1.</li> </ul>                                                                                                                                         | nuRadio platform<br>eceiver architecture<br>ustom-made processing blocks<br>Receiver front-end                                                                                                                                                                                                                                                                 | . 44<br>. 45<br>. 45<br>. 45<br>. 46                                                         |

| <ul> <li>6.1. G</li> <li>6.2. R</li> <li>6.3. C</li> <li>6.3.1.</li> <li>6.3.2.</li> </ul>                                                                                                                         | nuRadio platform<br>eceiver architecture<br>ustom-made processing blocks<br>Receiver front-end<br>Matched Filtering                                                                                                                                                                                                                                            | . 44<br>. 45<br>. 45<br>. 45<br>. 46<br>. 47                                                 |

| <ul> <li>6.1. G</li> <li>6.2. R</li> <li>6.3. C</li> <li>6.3.1.</li> <li>6.3.2.</li> <li>6.3.3.</li> </ul>                                                                                                         | nuRadio platform<br>eceiver architecture<br>ustom-made processing blocks<br>Receiver front-end<br>Matched Filtering<br>Time synchronization                                                                                                                                                                                                                    | . 44<br>. 45<br>. 45<br>. 45<br>. 46<br>. 47<br>. 48                                         |

| <ul> <li>6.1. G</li> <li>6.2. R</li> <li>6.3. C</li> <li>6.3.1.</li> <li>6.3.2.</li> <li>6.3.3.</li> <li>6.3.4.</li> </ul>                                                                                         | nuRadio platform<br>eceiver architecture<br>ustom-made processing blocks<br>Receiver front-end<br>Matched Filtering<br>Time synchronization<br>Coarse Frequency offset estimation                                                                                                                                                                              | . 44<br>. 45<br>. 45<br>. 45<br>. 46<br>. 47<br>. 48<br>. 49                                 |

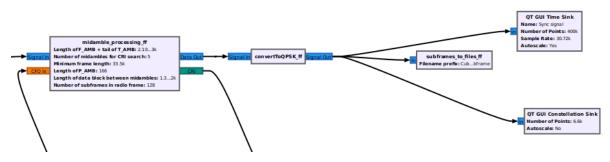

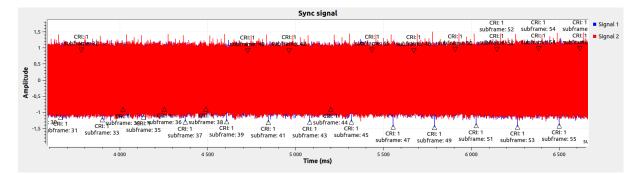

| <ul> <li>6.1. G</li> <li>6.2. R</li> <li>6.3.1.</li> <li>6.3.2.</li> <li>6.3.3.</li> <li>6.3.4.</li> <li>6.3.5.</li> </ul>                                                                                         | nuRadio platform<br>eceiver architecture<br>ustom-made processing blocks<br>Receiver front-end<br>Matched Filtering<br>Time synchronization<br>Coarse Frequency offset estimation<br>Midamble processing and frame disassembly part                                                                                                                            | . 44<br>. 45<br>. 45<br>. 45<br>. 46<br>. 47<br>. 48<br>. 49<br>. 51                         |

| <ul> <li>6.1. G</li> <li>6.2. R</li> <li>6.3.1.</li> <li>6.3.2.</li> <li>6.3.3.</li> <li>6.3.4.</li> <li>6.3.5.</li> <li>6.3.5.1.</li> </ul>                                                                       | nuRadio platform                                                                                                                                                                                                                                                                                                                                               | . 44<br>. 45<br>. 45<br>. 45<br>. 46<br>. 47<br>. 48<br>. 49<br>. 51<br>. 51                 |

| <ul> <li>6.1. G</li> <li>6.2. R</li> <li>6.3.1. G</li> <li>6.3.2. G</li> <li>6.3.3. G</li> <li>6.3.4. G</li> <li>6.3.5. G</li> <li>6.3.5.1. G</li> <li>6.3.5.2. G</li> </ul>                                       | nuRadio platform<br>eceiver architecture<br>ustom-made processing blocks<br>Receiver front-end<br>Matched Filtering<br>Time synchronization<br>Coarse Frequency offset estimation<br>Midamble processing and frame disassembly part<br>Coding rate evaluation<br>Radio frame disassembly                                                                       | . 44<br>. 45<br>. 45<br>. 46<br>. 47<br>. 48<br>. 49<br>. 51<br>. 51<br>. 52                 |

| <ul> <li>6.1. G</li> <li>6.2. R</li> <li>6.3. C</li> <li>6.3.1.</li> <li>6.3.2.</li> <li>6.3.3.</li> <li>6.3.4.</li> <li>6.3.5.1.</li> <li>6.3.5.1.</li> <li>6.3.5.2.</li> <li>6.3.5.3.</li> </ul>                 | nuRadio platform<br>eceiver architecture<br>ustom-made processing blocks<br>Receiver front-end<br>Matched Filtering<br>Time synchronization<br>Coarse Frequency offset estimation<br>Midamble processing and frame disassembly part<br>Coding rate evaluation<br>Radio frame disassembly<br>Fine timing, phase and frequency offset estimation                 | . 44<br>. 45<br>. 45<br>. 46<br>. 47<br>. 48<br>. 49<br>. 51<br>. 51<br>. 52<br>. 52         |

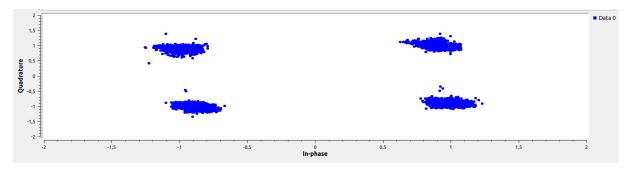

| <ul> <li>6.1. G</li> <li>6.2. R</li> <li>6.3. C</li> <li>6.3.1.</li> <li>6.3.2.</li> <li>6.3.3.</li> <li>6.3.4.</li> <li>6.3.5.1.</li> <li>6.3.5.1.</li> <li>6.3.5.2.</li> <li>6.3.5.3.</li> <li>6.3.6.</li> </ul> | nuRadio platform<br>eceiver architecture<br>ustom-made processing blocks<br>Receiver front-end<br>Matched Filtering<br>Time synchronization<br>Coarse Frequency offset estimation<br>Midamble processing and frame disassembly part<br>Coding rate evaluation<br>Radio frame disassembly<br>Fine timing, phase and frequency offset estimation<br>Demodulation | . 44<br>. 45<br>. 45<br>. 46<br>. 47<br>. 48<br>. 49<br>. 51<br>. 51<br>. 52<br>. 52<br>. 52 |

# List of acronyms

- BB Base-band

- CBSR C-band Satellite Radio

- DAC Digital to Analog Converter

- DMA Direct Memory Access

- FSM Finite State Machine

- NCBR Narodowe Centrum Badań I Rozwoju

- PA Power Amplifier

- PN Pseudorandom Noise

- PUT Poznań University of Technology

- SDR Software Defined Radio

- SR SatRevolution S.A.

- SoM System-on-Module

- SoC System-on-Chip

- t.b.d to be determined

# 1. Module Characteristics

#### 1.1. General Parameters

The CBSR receiver has been designed as the main component of the Cubesat ground station which was developed and implemented at PUT.

Based on the system specification presented in [1], the electrical parameters of the receiver are the following:

- carrier frequency user selectable between 5500 MHz and 6000 MHz, default 5840 MHz

- channel bandwidth user selectable: 1 MHz, 1.25 MHz, 5 MHz, 10 MHz, 20 MHz

- modulation type digital (quadrature) OQPSK

- channel coding Turbo, user selectable code rate: 0.19 0.91

- data/control interface RS-232, Ethernet

#### 1.2. Implementation

The receiver has been implemented using SDR technique, however, both "hardware oriented" and "software oriented" versions will be developed for system flexibility.

#### 1.2.1. "Hardware oriented" version

In "hardware oriented" version most of the receiver functionality is implemented using Xilinx Zynq7000 SoC based hardware platforms. Using the receiver Simulink model, developed in the project, the proprietary IP-cores are generated for Zynq7000 Programmable Logic (PL). Zynq7000 Processing System (PS) runs Linux applications which exchange data with the PL and perform non-time-critical operations.

The receiver implementation has been developed for two hardware platforms:

- ADRV9361 (a.k.a PicoZed) SoM featuring AD9361 transceiver IC and Zynq7035 device

- Mini-ITX board featuring Zynq7100 device with AD-FMCOMMS3 AD9361 evaluation module attached via FMC-LPC connector

The "hardware oriented" version performs real-time processing of the received signal, delivering the transmitted data "on-line" for the user in the ground station.

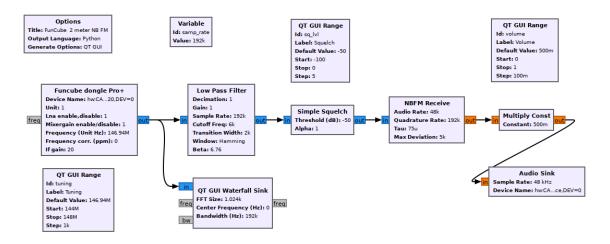

#### 1.2.2. "Software oriented" version

In "software oriented" version most of the receiver functionality is implemented using a highperformance PC running the software receiver based on GnuRadio platform. The RF part uses the offthe-shelf USRP B210 SDR hardware platform for signal reception and analog-to-digital conversion, attached to the PC via USB interface.

The "software oriented" version performs non-real-time processing of the received signal, delivering the transmitted data "off-line" for the user in the ground station.

# 2. Module Electrical Design - "hardware oriented" version

An efficient SDR implementation of the receiver requires application of an FPGA device. For this purpose a Xilinx ZYNQ System-on-Chip device, which combines dual-core ARM Cortex-A9 processor with the FPGA and a choice of interfaces was selected [2]. Most of the BB processing blocks are implemented in the FPGA, while the ARM processor is used for system control and management functions.

# 2.1. ADRV9361 based receiver

ADRV9361 is a Software Defined Radio (SDR) that combines the Analog Devices AD9361 integrated RF Agile Transceiver<sup>™</sup> with the Xilinx Z7035 Zynq<sup>®</sup>-7000 All Programmable SoC in a small system-on-module (SoM) footprint suitable for end-product integration.

The key features of the module [3] are listed below:

- Low-power Designed with a -2LI version of the Zynq SoC (low power, mid speed, industrial temp), DDR3L, and high-efficiency voltage regulators with margining capability to scale power with performance. Built-in sequencing and monitoring make it easy to power to the module.

- **High bandwidth data connectivity** Move data quickly with dual Gigabit Ethernet, USB2.0, four 6.6 Gb/s serial links (PCIe x4, SFP+, others), and high-speed LVDS I/O for custom interfaces.

- Wideband, frequency agile RF Uses the AD9361 to provide a highly integrated radio that enables wideband 2x2 MIMO receive and transmit paths from 70 MHz to 6.0 GHz with tunable channel bandwidth <200kHz to 56MHz.

- **Programmable SoC** Embedded processing with the Zynq Z-7035 SoC provides a Dual ARM<sup>®</sup> Cortex<sup>™</sup>-A9 MPCore<sup>™</sup> running at 800MHz, with built in peripherals like USB, Gigabit Ethernet, and memory interfaces.

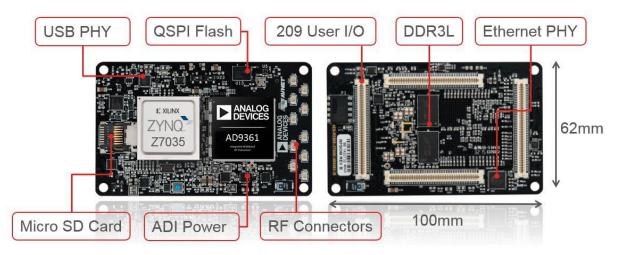

- Small form factor 100mm x 62mm footprint.

- **Production-ready module** System-on-Module designed for immediate prototype and quick integration in your end application. Industrial temperature rated and tested against MIL-STD 202G methods for Thermal, Vibration, and Shock.

- **Operating systems** Comes with Analog Devices Linux reference design for Zynq, bootable from an SD card. Also supports Linux, Android, FreeRTOS, eCos, VxWorks, and others not listed here.

- Development tools A broad range of SDR prototype and development environments are supported, including Analog Devices Linux Applications, and MATLAB<sup>®</sup> and Simulink<sup>®</sup> for data streaming and Zynq targeting.

- **Open-source code** Analog Devices provides precompiled reference designs on their PicoZed SDR wiki page and a source code support package hosted on Github, including the HDL and software code (except non-ADI).

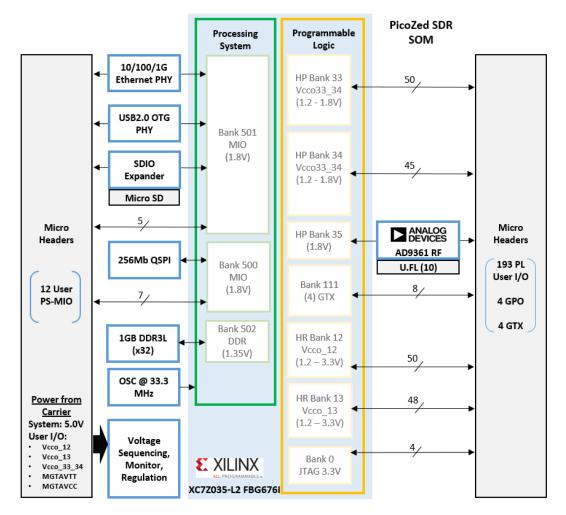

ADRV9361 module block diagram is depicted in Fig. 2.1 and Fig. 2.2 shows its layout.

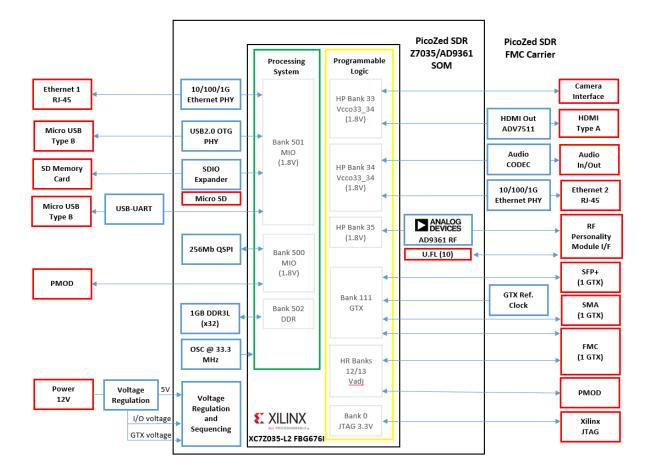

ADRV9361 can not work as a stand-alone module, it requires a corresponding carrier card. For this purpose the ADRV1CRR-FMC (a.k.a AES-PZSDRCC-FMC-G) carrier is used. The card gives designers access to a wide variety of peripherals and user I/O required to evaluate and develop with ADRV9361 SoM. The carrier card provides all necessary SoM power, reset control, and Zynq SoC I/O pin accessibility through the board-to-board (B2B) micro headers (see Fig. 2.3, 2.4).

Fig. 2.1 ADRV9361 SoM block diagram

Fig. 2.2 ADRV9361 SoM device layout

Fig. 2.3 ADRV1CRR-FMC carrier card block diagram

Fig. 2.4 ADRV1CRR-FMC carrier card layout

# 2.2. Xilinx Zynq Mini-ITX based receiver

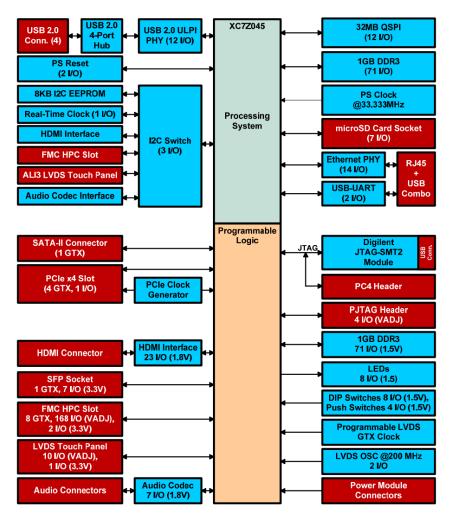

The Xilinx Zynq Mini-ITX Development Kit provides a complete development platform for designing and verifying applications based on the Xilinx Zynq-7000 All Programmable SoC family. Available with the Zynq XC7Z045-2FFG900 or the XC7Z100-2FFG900 device in a small Mini-ITX form factor, the kit enables designers to prototype high-performance designs with ease, while providing expandability and customization through the FMC HPC expansion slot. The Zynq Mini-ITX development board features consist of:

- Xilinx Zynq Z7100 SoC

- 1GB PS DDR3 SDRAM

- 1GB PL DDR3 SDRAM

- 32MB of QSPI Flash

- 8KB of I2C EEPROM

- Real-Time Clock

- 10/100/1000 Ethernet Interface

- USB-UART Interface

- microSD Card Interface

- USB 2.0 4-Port Hub

- PCIe x4 Root-Port (x16 physical Slot)

- SATA-III Interface

- FMC HPC Slot (VADJ of 1.8V, 2.5V, or 3.3V)

- SFP Socket

- LVDS Touch Panel Interface

- HDMI Interface

- Audio Codec

- User LEDs and Switches

- Programmable LVDS Clock Source (GTX reference clock)

- 200 MHz LVDS Oscillator (system clock)

- JTAG Header

The Mini-ITX Development Kit block diagram is depicted in Fig. 2.5.

The on-board FMC slot is used to connect to the AD-FMComms3-EBZ transceiver board. It provides AD9361 based RF platform, a highly integrated radio that enables wideband 2x2 MIMO receive and transmit paths from 70 MHz to 6.0 GHz with tunable channel bandwidth <200kHz to 56MHz.

The Mini-ITX platform, including the RF part, is shown in Fig. 2.6. The boards are mounted in a Mini-ITX format enclosure, together with a power supply.

Fig. 2.5 Mini-ITX Development Kit block diagram

Fig. 2.6 Mini-ITX SDR platform

# 3. Module Electrical Design - "software oriented" version

The "software oriented" receiver is designed for low-cost applications, e.g. at supporting ground stations which do not require on-line decoding of the transmitted data.

## 3.1. USRP B210 hardware platform []

The USRP B210 provides a fully integrated, single-board, Universal Software Radio Peripheral (USRP<sup>™</sup>) platform with continuous frequency coverage from 70 MHz – 6 GHz. Designed for low-cost experimentation, it combines the AD9361 RFIC direct-conversion transceiver providing up to 56MHz of real-time bandwidth, an open and reprogrammable Spartan6 FPGA, and fast SuperSpeed USB 3.0 connectivity with convenient bus-power. Full support for the USRP Hardware Driver<sup>™</sup> (UHD) software allows you to immediately begin developing with SDR software environment, e.g. GNU Radio.

The integrated RF frontend on the USRP B210 is designed with the new Analog Devices AD9361, a single-chip direct-conversion transceiver, capable of streaming up to 56 MHz of real-time RF bandwidth. The B210 uses both signal chains of the AD9361, providing coherent MIMO capability. Onboard signal processing and control of the AD9361 is performed by a Spartan6 XC6SLX150 FPGA connected to a host PC using SuperSpeed USB 3.0. The USRP B210 real time throughput is benchmarked at 61.44MS/s quadrature, providing the full 56 MHz of instantaneous RF bandwidth to the host PC for additional processing.

Since the receiver uses a single receive channel, a simpler (and cheaper) USRP B200 platform can be used without any degradation.

Fig. 2.7 USRP B210 hardware platform

# 4. Receiver implementation – PL part (FPGA) for "hardware oriented" version

## 4.1. Simulink model

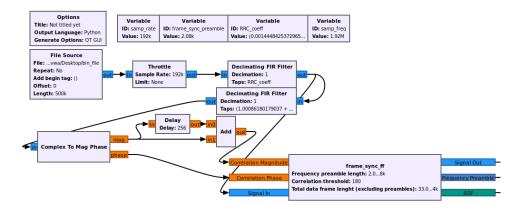

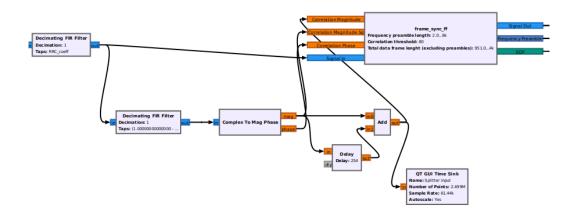

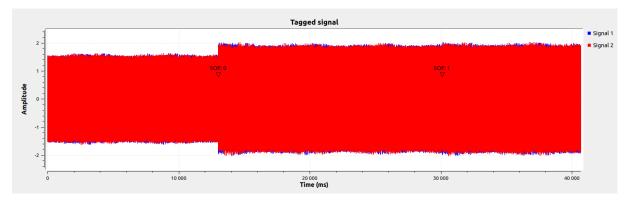

The receiver implementation in FPGA is prepared similarly to the transmitter with the help of Matlab/Simulink and its HDL Coder toolbox. In Fig. 4.1 the receiver block inputs and outputs are presented, the relevant ones are described in Table 4.1.

|   | Receiver v16         |                           |  |

|---|----------------------|---------------------------|--|

|   |                      |                           |  |

| > | rx_l                 |                           |  |

| 、 | rx Q                 | data_out                  |  |

| 1 | ix_Q                 | valid_out<br>MAGIC NUMBER |  |

| > | valid_in             | ENABLE_REG_rb             |  |

|   | -                    | RADIO CONFIG REG rb       |  |

| > | ENABLE_REG           |                           |  |

| 、 |                      | NUM_RF_SUBFRAMES_REG_rb   |  |

| 1 | RADIO_CONFIG_REG     | SYNC_THR_VAL_REG_rb       |  |

| 5 | NUM RF SUBFRAMES REG | ZTEST_BIT_MASK_rb         |  |

| 1 |                      | ZTEST_FIXED_POINT_rb      |  |

| > | SYNC_THR_VAL_REG     | ZTEST_REG32BIT_rb         |  |

|   |                      | BIT_COUNT_REG_L           |  |

| 2 | ZTEST_BIT_MASK       | BIT_COUNT_REG_H           |  |

| • | ZTEST FIXED POINT    | BIT_ERR_COUNT_REG_L       |  |

| 1 |                      | BIT_ERR_COUNT_REG_H       |  |

| > | ZTEST_REG32BIT       | SUBFRAME_COUNT_REG        |  |

| ĺ |                      | SUBFRAME_ERR_COUNT_REG    |  |

| > | ZTEST_REG64BIT_L     | ZTEST_REG64BIT_L_rb       |  |

| > | ZTEST REG64BIT H     | ZTEST_REG64BIT_H_rb       |  |

| 1 |                      |                           |  |

|   |                      |                           |  |

Fig. 4.1 Receiver block

| Name                   | Туре             | Description                                                                                                                                                                                                                                                                                       |

|------------------------|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| rx_l/rx_Q              | Input            | Receivers' in-phase and quadrature component samples                                                                                                                                                                                                                                              |

| valid_in               | Input            | Valid signal for ADC samples                                                                                                                                                                                                                                                                      |

| ENABLE_REG             | Input/<br>Output | Register that stores i.a. a value that enables/disables the receiver. When its state is high, the signal can be received, when it's low the receiver will stop collecting samples on its input                                                                                                    |

| RADIO_CONFIG_REG       | Input/<br>Output | <ul> <li>A register used to set:</li> <li>the transmission mode (described in [3])</li> <li>the roll-off factor of the shaping RRC filter. There are 2 settings available i.e. 0 and 1.</li> <li>the length of the frequency offset estimation part of the preamble (described in [3])</li> </ul> |

| NUM_RF_SUBFRAMES_REG   | Input/<br>Output | Sets the number of subframes in each radio frame.                                                                                                                                                                                                                                                 |

| data_out               | Output           | 32-bit data words                                                                                                                                                                                                                                                                                 |

| valid_out              | Output           | Indication whether output data is valid                                                                                                                                                                                                                                                           |

| SUBFRAME_COUNT_REG     | Output           | The number of received subframes                                                                                                                                                                                                                                                                  |

| SUBFRAME_ERR_COUNT_REG | Output           | The number of erroneous subframes                                                                                                                                                                                                                                                                 |

| BIT_COUNT_REG          | Output           | The number of received bits in transmission modes 1 and 2                                                                                                                                                                                                                                         |

|                   | Quitaut | The number of erroneous bits in transmission modes |  |

|-------------------|---------|----------------------------------------------------|--|

| BIT_ERR_COUNT_REG | Output  | 1 and 2                                            |  |

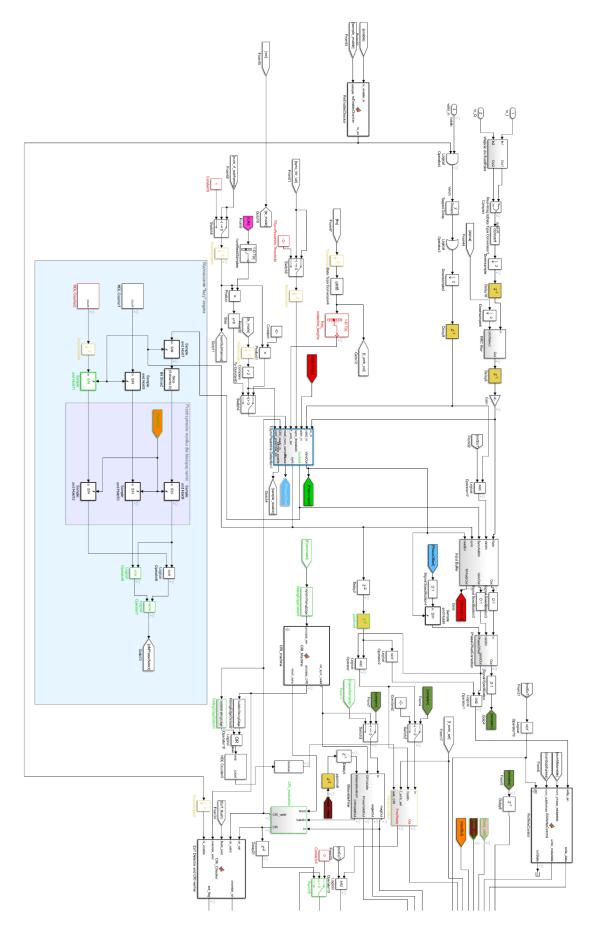

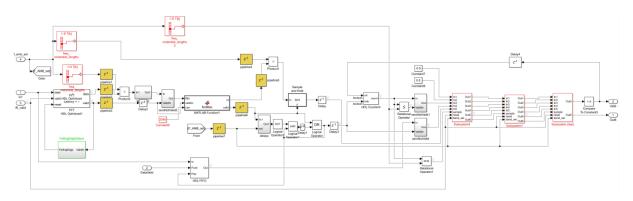

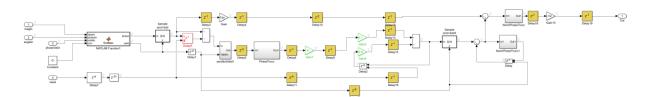

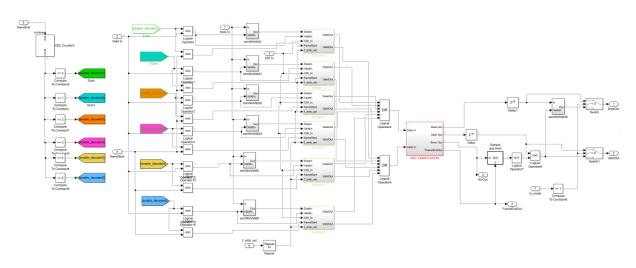

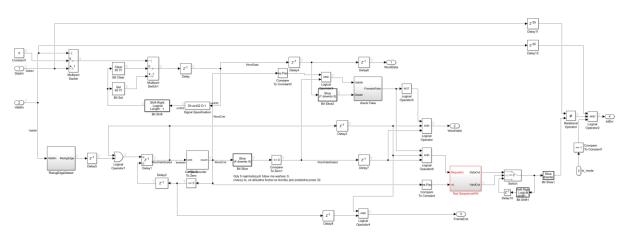

In Fig. 4.2 and Fig. 4.3. the general structure of the receiver is presented. The main components of the receiver are shown and described in detail in the subsequent sections.

Fig. 4.2 Overview of the receiver Simulink schematics - part 1

Fig. 4.3 Overview of the receiver Simulink schematics - part 2

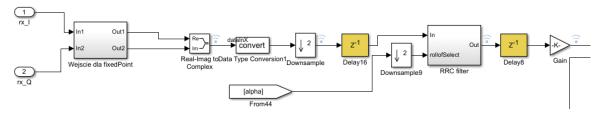

## 4.1.1. Matched Filtering

The operations performed in the receiver are the inversion of those performed in the transmitter. The first part of the receiver (depicted in Fig. 4.4.) is responsible for filtering received signal samples with a matched RRC filter. The output samples from the filter are stored in an input buffer (*Input Buffer* block in Fig. 4.2) but also fed into a signal detection and time synchronization block named *TSyncPreambleDetection*

Fig. 4.4 Matched filtering

### 4.1.2. Time synchronization

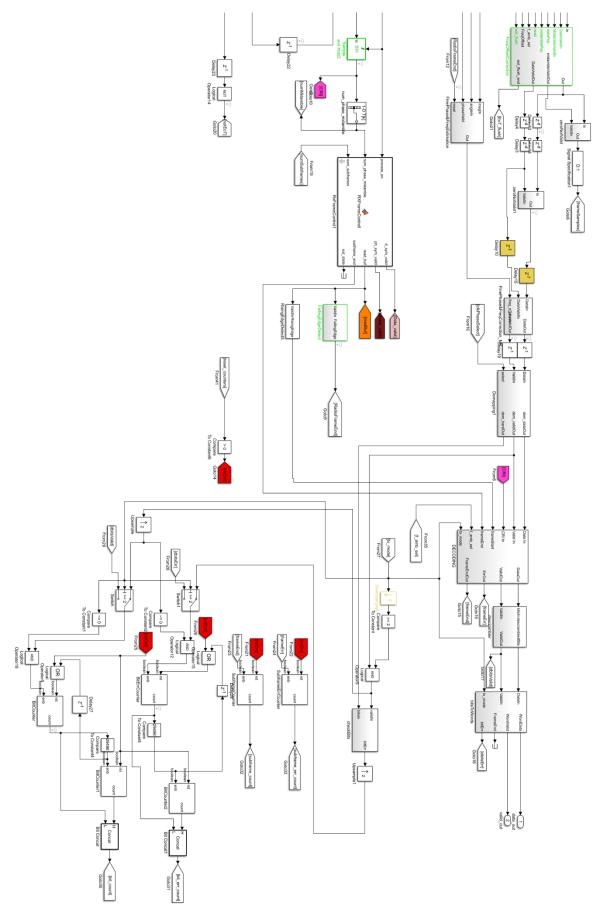

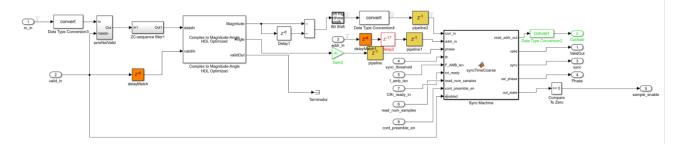

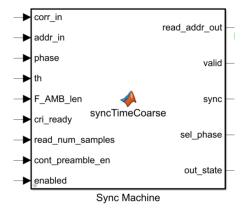

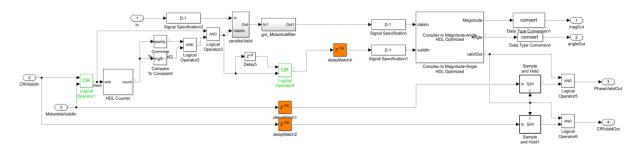

The internal structure of the detection and time synchronization block is shown in Fig. 4.5. The input samples are first filtered with a FIR filter with coefficients matching the Zadoff-Chu sequence used in the *T\_AMB* part of the preamble. The output of the filter is fed into a magnitude and phase calculation block. The magnitude is used to construct a correlation metric used for signal detection and time synchronization, whereas the phase is used for initial coarse phase offset estimation. The main part of the synchronization subsystem is the *Sync Machine* FSM (Fig. 4.6). The inputs and outputs of this block are shown and described in Table 4.2.

Fig. 4.5 Signal detection and time synchronization

The main task of the *Sync Machine* block is to find the address in the input buffer for which the correlation metric is the highest (assuming that it is higher than the threshold). When the peak in correlation value has been found the *Sync Machine* starts the process of reading samples from the input buffer. The output from the buffer is fed into several subsystems that perform operations such as coarse frequency offset estimation and coding rate estimation, simultaneously/

Fig. 4.6 Sync Machine FSM

| Table 4.2 Selected In | nuts and outputs  | of Sunc Machina   |

|-----------------------|-------------------|-------------------|

| Table 4.2 Selected In | iputs and outputs | OI SYNC IVIUCIIII |

| Name             | Туре   | Description                                                                                                                                                                                                                              |

|------------------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| corr_in          | Input  | Received signal correlation metric used for signal detection and time synchronization                                                                                                                                                    |

| addr_in          | Input  | Current write address in the input buffer                                                                                                                                                                                                |

| phase            | Input  | Received signal phase metric used for initial phase offset estimation                                                                                                                                                                    |

| th               | Input  | A threshold value for signal detection                                                                                                                                                                                                   |

| F_AMB_LEN        | Input  | The length of the preamble used for frequency offset estimation                                                                                                                                                                          |

| cri_ready        | Input  | Indication whether the coding rate has been evaluated                                                                                                                                                                                    |

| read_num_sampels | Input  | Number of samples to read from the input buffer before the next signal detection window                                                                                                                                                  |

| cont_preamble_en | Input  | Used to enable continuous preamble mode in the synchronization block                                                                                                                                                                     |

| enabled          | Input  | A line used to enable/disable synchronization is related to the enable signal of the receiver                                                                                                                                            |

| read_addr_out    | Output | Current read address from the input buffer                                                                                                                                                                                               |

| valid            | Output | A signal indicating that the output samples of the input buffer are valid                                                                                                                                                                |

| sync             | Output | A signal indicating that radio frame has been detected. The samples output by the input buffer when this signal is high are fed into a coarse frequency offset estimation block. These samples belong to the F_AMB part of the preamble. |

| sel_phase        | Output | Initial coarse phase offset estimate                                                                                                                                                                                                     |

#### 4.1.3. Coarse Frequency offset estimation

The first *F\_AMB\_len* samples from the input buffer are used for coarse frequency offset estimation. The goal of this subsystem is to mitigate the effect of a frequency shift. The main source of this shift is the Doppler effect, which impact is also mitigated outside of the receiver implementation, and this subsystem was designed to reduce the impact of any leftover shift that wasn't already compensated.

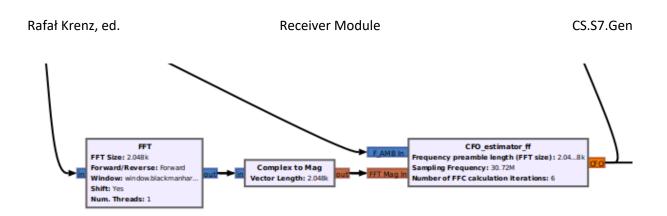

The internal structure of the coarse frequency offset estimation is shown in Fig. 4.7. Its operation is based on performing FFT on  $F_AMB$  preamble samples. The index of the maximum magnitude value of the FFT outcome and the  $F_AMB$  preamble samples are used for calculating metrics used for frequency offset estimation. The detailed algorithm was described in the report [4].

Fig. 4.7 Frequency offset estimation

# 4.1.4. Coding rate evaluation

The information about the coding rate used in the transmitter is carried by a phase midamble. Each coding rate has its own form of midamble created by performing a cyclical shift on a base Zadoff-Chu sequence. In order to correctly disassemble the received radio frame the correct value of the coding rate used in the transmitter is essential. Hence, the coding rate has to be known before we can process the radio frame. The block responsible for evaluating the coding rate is shown in Fig. .4.8. It operates on the samples coming from a midamble filter subsystem shown in Fig. 4.9. The filter subsystem performs filtering with base Zadoff-Chu coefficients and the magnitude of the filtered samples is used in the *CRI evaluation* subsystem. In the evaluation, we search for the sample index for which the magnitude is maximal. This index is fed into a post-processing system responsible for converting it to the coding rate indicator in the range from 0 to 7 (where values 0-6 denotes valid coding rates and value 7 denotes the EoT frame).

Fig. 4.8 Coding rate evaluation

Fig. 4.9 Midamble filter

#### 4.1.5. Radio frame disassembly

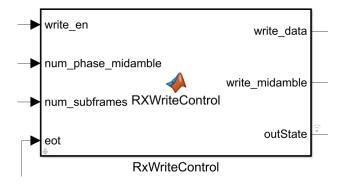

The samples coming from the input buffer are stored in dedicated queues (in the frequency offset correction block), where they wait for the coding rate evaluation and coarse frequency offset estimation to finish their processing. There is one queue for the data symbols and one for midamble symbols. The write operation to each of the queues is managed by a controller depicted in Fig. 4.10. The inputs and outputs of this controller are described in Table 4.3.

Fig. 4.10 Write controller

| Table 4.3 Inputs and outputs F | RxWriteControl block |

|--------------------------------|----------------------|

|--------------------------------|----------------------|

| Name               | Туре   | Description                                                    |

|--------------------|--------|----------------------------------------------------------------|

| write en           | Input  | A line indicating that samples are valid and can be written to |

| write_en input     |        | processing queues                                              |

| num_phase_midamble | Input  | A line that specifies the number of phase midambles in         |

| num_phase_midumble | mput   | subframe (evaluated based on coding rate)                      |

| num_subframes      | Input  | Number of subframes in radio frame                             |

|                    | Input  | A line indicating that EoT frame has been received and no      |

| eot                |        | further write operation is allowed until the next reception    |

|                    |        | session.                                                       |

| write data         | Output | A line indicating that the currently processed sampes should   |

| write_ddid         | Output | be written to data samples queue                               |

| write midamble     | Output | A line indicating that the currently processed sampes should   |

| write_iiliddifible |        | be written to midamble samples queue                           |

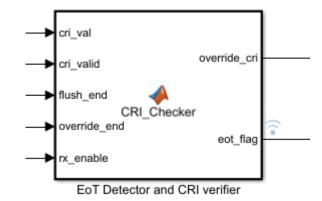

The evaluated coding rate value is fed to a EoT Detector and CRI verifier controller (Fig. 4.11), which task is to analyze the coding rate value and recognize the EoT frame and also check whether the coding rate value is in the allowed range of 0 to 6. The inputs and outputs of the controller are described in Table 4.4.

In the case that the EoT frame is recognized the controller indicates the fact by setting the *eot\_flag* which will disable some parts of the receiver until the next reception session is started. If the controller detects that the coding rate value is outside the allowed range an *override\_cri* signal is set which will cause the receiver to use the default coding rate value which is 0. The frame where the coding rate evaluation is incorrect will be lost.

Fig. 4.11 EoT detector and coding rate verifier

| Name          | Туре   | Description                                                                                                      |

|---------------|--------|------------------------------------------------------------------------------------------------------------------|

| cri_val       | Input  | Currently estimated coding rate value                                                                            |

| cri_valid     | Input  | A line indicating that the cri_val is valid                                                                      |

| flush_end     | Input  | A line indicating that the EoT procedure has been completed                                                      |

| override_end  | Input  | A line used to reset coding rate override in the case that the coding rate evaluation resulted in invalid value  |

| rx_enable     | Input  | An indication whether the receiver is enabled.                                                                   |

| override_flag | Output | A line indicating that the evaluated coding rate value is invalid and should be replaced with default value of 0 |

| eot_flag      | Output | A line indicating that the EoT frame has been detected used to start the EoT procedure                           |

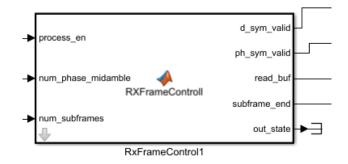

When the frequency offset estimation and coding rate evaluation are done, the samples stored in the data and midamble queues can be read and coarse frequency correction can be performed on these samples. The read process is controlled by the *RxFrameControl* block depicted in Fig. 4.12. The inputs and outputs of the controller are described in Table 4.5.

The samples coming from the midamble queue are fed into a midamble filter subsystem described in section 4.1.4, where the magnitude and phase of the filtered samples are calculated. The results are fed into a fine frequency and phase offset estimation block.

The samples coming from the data symbols queue are fed into fine frequency and phase offset correction block where the offsets are compensated and the result is fed into a demodulator.

Fig. 4.12 RxFrameControl block

| Table 4.5 Inpu | its and outputs | of RxFrameContro | ol block |

|----------------|-----------------|------------------|----------|

|----------------|-----------------|------------------|----------|

| Name               | Туре   | Description                                                                                                                                       |  |  |  |

|--------------------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| process_en         | Input  | A line indicating that coarse frequency offset estimation has<br>been completed and the ramining part of the received<br>samples can be processed |  |  |  |

| num_phase_midamble | Input  | A line that specifies the number of phase midambles in subframe (evaluated based on coding rate)                                                  |  |  |  |

| num_subframes      | Input  | Number of subframes in radio frame                                                                                                                |  |  |  |

| d_sym_valid        | Output | A line indicating that the data samples should be read from processing queues                                                                     |  |  |  |

| ph_sym_valid       | Output | A line indicating that the midamble samples should be read from processing queues                                                                 |  |  |  |

| read_buf           | Output | A line indicating that samples should be read from processing queues                                                                              |  |  |  |

| subframe_end       | Output | A line indicating the end of a subframe                                                                                                           |  |  |  |

# 4.1.6. Fine phase and frequency offset estimation

The fine phase and frequency offset estimation subsystem is depicted in Fig. 4.13. It accepts magnitude and phase values calculated by the midamble filter described in section 4.1.4. The offsets are calculated for the phase value for which the magnitude had a maximal value. The exact algorithm is described in the report [4].

Fig. 4.13 Fine phase and frequency offset estimation

# 4.1.7. Demodulation

The demodulation of the OQPSK symbols is performed in the subsystem shown in Fig. 4.14. The OQPSK symbol is first converted to a QPSK equivalent by delaying the real component of the symbol by half the base sampling rate of the modulated signal. The QPSK symbols are then mapped to a likelihood metrics that can be used in the decoder.

Fig. 4.14 demodulation subsystem

#### 4.1.8. Decoding

The decoding subsystem is depicted in Fig. 4.15. It consists of a set of parallel turbo decoders. The need for more than one decoder is due to the fact that the processing delay of a single instance is too high and a single decoder would not be able to decode all the received subframes in time. Based on a thorough analysis the number of required decoders was set to 6. The decoders are run in a sequential manner and are configured in such a way that the output from each does not overlap with others, hence there is no need to add more than one CRC verification block. The CRC verification block is responsible for checking the CRC of the received data and indicating whether it is correct or not. The data with the error flag is discarded in transmission mode 0. However, for transmission mode 1 the erroneous data is analyzed and error statistics are gathered.

Fig. 4.15 Decoding subsystem

## 4.1.9. Data packing

The final step in the receiver processing chain is the data packing operation. The block responsible for this task is depicted in Fig. 4.16. Its main goal is to convert bits into 32-bit words that are accepted by the software. In addition, this block is also responsible for detecting fake subframes which are either discarded in transmission mode 0 or analyzed for bit errors in transmission mode 1.

Fig. 4.16 Data packing subsystem

#### 4.2. Custom-made IP cores

#### 4.2.1. Introduction

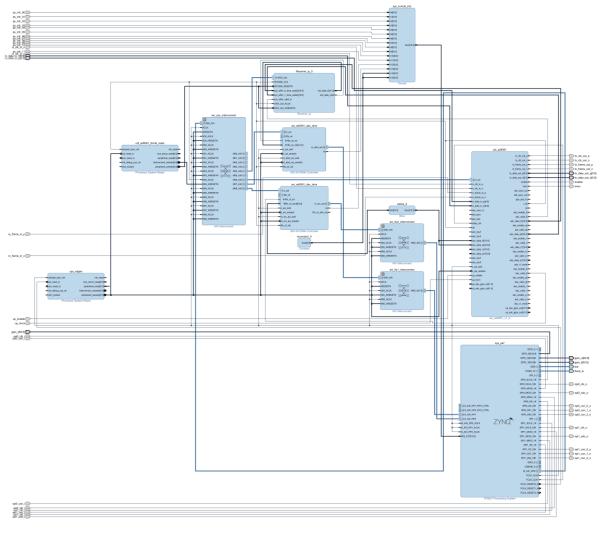

The FPGA-based signal processing routine, created with the aid of MATLAB HDL Coder, is encapsulated into a user-developed Vivado IP core. To incorporate a receiver IP core into a Vivado block diagram, a Matlab HDL workflow coder is used. The workflow operates according to a given so-called reference design, which specifies the Vivado block diagram, the way in which the custom-made IP core is merged with it, and the board pin assignment (constraint file). The reference designs have a form of TCL scripts. In the current project, a reference design by Analog Devices, dedicated to Mini-ITX device, equipped with Xilinx Zynq®-7000 All Programmable SoC XC7Z045 and an FMC2/3/4 transceiver card with AD9361, is used as a baseline. The device used in the project is Mini-ITX with XC7Z100 plus the FMC2/3/4 card, so the reference design seems to be most accurate in the cases where the IQ samples (for 2 receiver channels) are conveyed through PL directly to PS since there are four interleaved 16-bit data lines on the PL to PS interface. Signal processing in PL is an option (the user-specified IP core can be by-passed in some cases).

In the current project, the data transferred from PL to PS via DMA have the meaning of binary vectors instead of complex IQ samples; the data rate on the PL<>PS interface is significantly smaller than the symbol rate on the SoC<>AD9361 interface as there is nothing else but PL responsible for the physicallayer signal processing (frame detection, demodulation, channel estimation, channel decoding, descrambling, etc.). As a consequence, it is more accurate to consider only one wide data line on the PL<>PS interface. The data vectors to be transferred to PS via DMA are generated asynchronously once a new frame has been acquired and decoded with no errors. For that reason it is necessary to wire a "data valid" line along with the data line.

Another problem to be solved when using MiniITX-XC7Z100 part is that Vivado has been lacking its definition for a few years. To overcome that issue, some tweaks in Vivado installation are necessary. Making them results with appearance of MiniITX-XC7Z100 part on a board selection pane (see Fig. 4.17) and xc7z100ffg900-2 SoC in project settings (Fig. 4.18)

#### 4.2.2. Reference design customization

With the aim to overcome the disadvantages of the original reference design, the datapath is significantly modified. Four 16-bit data lines have been replaced with one 32-bit data line. Consequently, data streams are not interleaved anymore (interleaving required troublesome synchronization between the streams), so the blocks responsible for stream interleaving and deinterleaving are removed. The *utility\_buffer* IP, originally placed between FIFO at the clock domains' border and the DMA interface, has been removed. It was devoted to alleviate the problem of asynchronous type of data feed through DMA interface, but it has appeared to cause highly undesired random delays.

| 🍌 Select Device                      |                                |                  |                  |                   |               |              |               |      | <b>—</b> ×- |

|--------------------------------------|--------------------------------|------------------|------------------|-------------------|---------------|--------------|---------------|------|-------------|

| Filter, search, and b                | prowse parts by their resource | s. The selection | will be applied. |                   |               |              |               |      | 4           |

| Select: 🔷 Parts<br>4 Filter/ Preview | 🗧 Boards                       |                  |                  |                   |               |              |               |      |             |

| Ve <u>n</u> dor:                     | All                            | 1                |                  |                   |               |              |               |      |             |

| Display Name:                        | All                            | ī                |                  |                   |               |              |               |      |             |

| Board Rey:                           | Latest 👻                       | 1                |                  |                   |               |              |               |      |             |

|                                      | Reset All Filters              |                  |                  |                   |               |              |               |      |             |

|                                      |                                | _                |                  |                   |               |              |               |      |             |

| Search: Q-                           |                                | •                |                  |                   |               |              |               |      |             |

| Display Name                         |                                | Vendor           | Board Rev        | Part              | I/O Pin Count | File Version | Block<br>RAMs | DSPs | FlipFlops   |

| 📓 ZYNQ-7 Mini-ITX                    | Motherboard XC7Z045            | em.avnet.com     | D                | 🔷 xc7z045ffg900-2 | 900           | 1.2          | 545           | 900  | 437200      |

|                                      | Motherboard XC7Z100            | em.avnet.com     |                  | 🔷 xc7z100ffg900-2 | 900           | 1.0          | 755           | 2020 | 554800      |

| 📲 ZedBoard Zyng B                    | Evaluation and Development Ki  | t em.avnet.com   | d                | 🔷 xc7z020clg484-1 |               | 1.3          | 140           | 220  | 106400      |

| 📲 ZYNQ-7 ZC702 E                     | valuation Board                | xilinx.com       | 1.0              | 🔷 xc7z020clg484-1 | 484           | 1.2          | 140           | 220  | 106400      |

| 📓 ZYNQ-7 ZC706 E                     | valuation Board                | xilinx.com       | 1.1              | 🔷 xc7z045ffg900-2 | 900           | 1.3          | 545           | 900  | 437200      |

|                                      |                                |                  |                  |                   |               |              |               |      |             |

| •                                    | III                            |                  |                  |                   |               |              |               |      | *           |

| ?                                    |                                |                  |                  |                   |               |              |               | ОК   | Cancel      |

|                                      |                                |                  |                  |                   |               |              |               |      |             |

Fig. 4.17 Device selection window in Vivado with the desired board included

|                                                      | General                                                                                                                                                                                                                                                |     |

|------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| General<br>Concernation<br>Simulation<br>Elaboration | Name:     vivado_prj       Project device: <ul> <li>xc7z100ffg900-2 (active)</li> <li>Iarget language:</li> <li>Verilog</li> <li>Default library:</li> <li>xil_defaultlib</li> <li>Top module name:</li> <li>system_top</li> <li>System_top</li> </ul> | •   |

| Synthesis<br>Implementation<br>Bitstream<br>IP       | Language Options: verilog_version=Verilog 2001                                                                                                                                                                                                         |     |

| ?                                                    | OK Cancel Ap                                                                                                                                                                                                                                           | ply |

Fig. 4.18 Desired SoC version shown in the project settings

The genuine reference design by Analog Devices features more IP cores useless from the perspective of the current project. In particular, it refers to the IP cores playing the role of HDMI, SPDIF, and I2S interfaces; their removal brings reasonable FPGA resources savings. Note that removing unnecessary IP cores involves modification of both wrapper- and system top HDL files.

Some minor changes, shown in Fig. 4.19, have been made in the settings of *axi\_ad9361* IP core, responsible for transferring IQ passband signal samples, received by AD9361, to FPGA.

| Re-customize IP                        | . (1.0)                                            |                          |                    |

|----------------------------------------|----------------------------------------------------|--------------------------|--------------------|

| кi_ad9361_v1_0                         | J (1.U)                                            |                          | I                  |

| Documentation 🛅 IP Le                  | ocation                                            |                          |                    |

| Show disabled ports                    |                                                    | Component Name system_   | _axi_ad9361_0      |

|                                        | to all out a                                       | Adc Dataformat Disable   | 0 💿                |

|                                        | tu_cli_out_n=<br>tu_fiane_out_p=                   | Adc Datapath Disable     | 0                  |

|                                        | ts_frame_ost_n                                     | Adc Dcfilter Disable     | 0 🛞                |

| نمردا                                  | ts_data_out_p[5:0] =<br>ts_data_out_n[5:0] =       | Adc Init Delay           | 20                 |

| - welking                              | erable                                             | Adc Igcorrection Disable |                    |

| - w_skin_n<br>- w_fiame_in_p           | dac_sync_out =<br>tobj_sync_out =                  | Adc Userports Disable    | 0                  |

| = u_fiame_in_n<br>■ u, data in p(S:0)  | gps_pps_ing                                        | Cmos Or Lvds N           | 0                  |

| ■u_data_iq_q[S:0]<br>=dat_sγat_in      | Lok -<br>at -                                      | Dac Clk Edge Sel         |                    |

| =tdd_sync                              | adc_enable_0=<br>adc_valid_0=                      | Dac Datapath Disable     |                    |

| -delay_cik                             | adt_clata_0(15:0) =<br>adt_castle_c0=              | Dac Dds Disable          |                    |

| −clt.<br>−ødc_dov/                     | adc_vaid_q0 =<br>adc_data_q0[15:0] =               |                          |                    |

| = ack_dusf<br>= dac_data_20[15:0]      | adc_enable_1                                       | Dac Init Delay           | 0                  |

| dat_data_q0[15:0]<br>dat_data_11[15:0] | adc_vaid_i1=<br>adc_data_i1(15:0) =                | Dac Iodelay Enable       | 0                  |

| ■dac_data_q1[15:0]                     | ado_enable_q1 =<br>ado_vaid_q1 =                   | Dac Iqcorrection Disable | a 0 💿              |

| ≕dac_dov/<br>—dac_dov/                 | att_data_q1[15:0] =<br>att_1 mode                  | Dac Userports Disable    | 0 8                |

| -s_axi_acti<br>-Sa axi ansata          | dat_enable_i0                                      | Device Type              | 0                  |

| -up_enable<br>-up_tana                 | dac_vaFd_0<br>dac_enable_q0                        | Id                       | 0                  |

| up_dec_gpio_in[31:0]                   | dac_vafd_q0 =<br>dac_enable_i1 =                   | Io Delay Group           | dev_jf_delay_group |

| up_adc_gpoql31:0                       | dac_vaiid_i1<br>dac_enable_g1                      | Mode 1r1t                | 1 0                |

|                                        | dat_vaid_q1=<br>dat_v1_mode=                       | Pps Receiver Enable      | 0 0                |

|                                        | up_dac_gpio_out[31:0] =<br>up_adc_gpio_out[31:0] = | Tdd Disable              |                    |

Fig. 4.19 Configuration window of axi\_ad9361 IP core

In detail, *1R1T mode* is chosen to eliminate redundant support for two receive channels (according to the project assumptions, only one receive channel is utilized). Additionally, *TDD disable* option is checked, since the AD9361 is forced to operate permanently in Rx mode by an SPI write to AD9361 registers instead of periodic Tx/Rx toggling, controlled via FPGA pins. Thanks to that, neither 24-bit TDD counter nor a few reference registers of the same size are implemented in FPGA. The rest of configuration fields of axi\_ad9361 IP core take the default values. DDS feature is enabled for testing purposes.

Another improvement has been made in the domain of custom-made IP core clocking. In the original reference design, the user's IP core is clocked by the AD9361 clock divided by 2 (or by 4 in the case of 2 transmit streams – not applicable to the current design). It limits the system capability of serial data processing, since half of the clock cycles are not usable. Instead, the custom-made IP core is now clocked with the original AD9361 clock (*rx\_clk*), distributed throughout the FPGA device directly from a respective BUFG element.

The decision to eliminate a separate clock domain for custom-made IP core results with a simpler clock cross-domain management: there is only one clock-domain crossing in the data path, handled safely by means of a FIFO in *axi\_ad9361\_adc\_dma* IP core. To transfer commands and status messages data between the time domains (*clk\_fpga\_0* and *rx\_clk*) through AXI4-Lite, a 3-stage synchronizer is placed in the *axi\_cpu\_interconnect* IP core. Together with AXI protocol handshaking, it guarantees safe transfers.

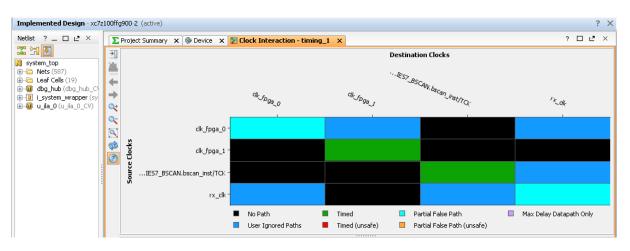

Taking into account asynchronous data transfer between the clock domains (for both data path and the control/status AXI channel), it is desired to constrain intra-clock paths on FPGA as false paths, thereby instructing the Vivado placer to ignore them; it helps overcome timing-related issues when routing. Fig. 4.20 proves that the paths between clock domains: *clk\_fpga\_0* and *rx\_clk* are successfully set as false paths in Vivado.

Fig. 4.20 Clock interaction report for the implemented design in Vivado

Not only is the MATLAB HDL workflow responsible for generating appropriate interfaces of the custommade IP core and incorporating it into the reference design, but also for attaching extraordinary constraint files to the project. The constraint files contain the settings related to the hardware pinout, clock frequency, false paths, etc. The pinout for MiniITX-XC7Z100 is identical as for MiniITX-XC7Z045, so the constraint files related to the pins' voltage and their assignment imported from the original reference design are kept untouched.

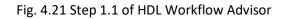

# 4.2.3. The use of Simulink HDL Workflow Advisor

To avoid compatibility issues with a quite outdated reference design for MiniITX-XC7Z045, the authors have decided to target their own MiniITX-XC7Z100 reference design for Vivado 2016.4. It has been integrated with the HDL Workflow of Matlab 2017b under the name of *MiniITX* – it should be chosen as the Target platform in Step 1.1 of the HDL Workflow Advisor, as shown in Fig. 4.21. Note that the accurate MiniITX device (xc7z100) is associated with it, automatically. As the result of researchers' efforts, Step 1.2 (shown in Fig. 4.22) enables setting specific board peripherals to be used or not. Thanks to that one can decide to activate: LEDs, buttons, or DIP switches to control or observe selected lines. According to his/her choice, one of alternative reference designs is loaded.

Step 1.3, shown in Fig. 4.23, brings the possibility to connect the inputs and outputs of the developed Simulink block diagram to appropriate reference design wires (aka target platform interfaces). Note the possibility to choose LEDs in the middle column. The use of board peripherals, like LEDs, buttons, DIP switches must match the choices made in Step 1.2. If not, an error message will appear. The meaning of specific target platform interfaces is explained in Table 4.6. It does not include the Simulink ports attached to the AXI4-Lite interface, used to send control commands from PS to PL and read diagnostic messages in the opposite direction.

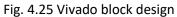

After passing checks in Steps 2.1-2.4, the HDL code for the custom-made IP core is generated in Step 3.2 of HDL Workflow Advisor. The generated IP core is deposited in a folder specified by the user and can be manually placed into any Vivado block diagram. However, the customized reference design *MiniITX* features the possibility to automatically integrate the IP core with the block diagram. It can be done in Step 4.1 of HDL Workflow Advisor. If the process ends successfully, a link to a new-created Vivado project appears in a log window of HDL Workflow Advisor, as shown in Fig. 4.24). Clicking the link launches Vivado and the project opens. It is not suggested to run remaining steps of HDL Workflow Advisor, as they are accurate only for the case when FPGA processing is controlled by Simulink (a kind of hardware-software co-simulation).

| ⊘ HDL Workflow Advisor - Cubesat_Rx11/Receive                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

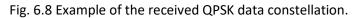

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|